### Mul tibank® DRAM (MDRAM®)

128Kx32 to 656Kx32

### Prel iminary Information

#### • Ultra-High Performance

666 MByte/sec single device transfer rate 36 ns RAS access, 13.8 ns CAS access 6 ns burst cycle

#### • Multibank Architecture

RAS and precharge may overlap CAS READ or WRITE to different banks effectively hiding RAS/precharge time.

#### • Ideal Organization for Embedded Applications

| Part Code | Organization | Banks | MBytes |

|-----------|--------------|-------|--------|

| MD904     | 128K x 32    | 16    | 0.5    |

| MD906     | 192K x 32    | 24    | 0.75   |

| MD908     | 256K x 32    | 32    | 1.0    |

| MD909     | 288K x 32    | 36    | 1.125  |

| MD910     | 320K x 32    | 40    | 1.25   |

| MD916     | 512K x 32    | 64    | 2.0    |

| MD918     | 576K x 32    | 72    | 2.25   |

| MD920     | 640K x 32    | 80    | 2.5    |

|           |              |       |        |

#### Fine Granularity

Quarter MByte minimum granularity facilitates precise sizing of memory to any 1/4 MByte size from 1/2 MByte and up.

#### Variable Length Burst

Supports 4 to 128 byte interruptable bursts

- Byte-level Write Control

- Low Internal and Interface Power.

- Small Footprint

Up to 2.3 MByte single package: 14 mm x 20 mm PQFP or 68 pin PLCC.

#### • Compact, Easily Implemented Interface

Twenty-six signal, bus interface employs CMOS/LVCMOS/SSTL signaling.

Both 5.0V and 3.3V Supply Option

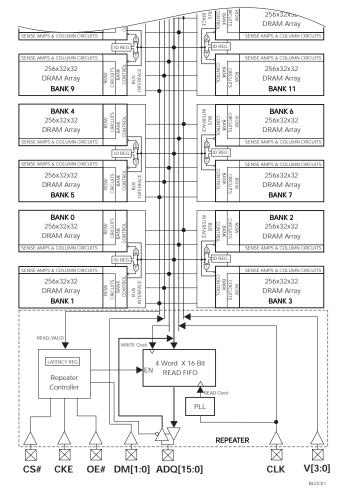

Figure 1. MDRAM Block Diagram

#### Description

The MoSys Multibank DRAM (MDRAM) is an extended performance synchronous DRAM optimized for ultra-high performance applications where high bandwidth, extremely short access latency and low cost are required. MDRAMs feature fully synchronous I/O at frequencies up to 333 MHz providing 666 MBytes per second of peak bandwidth.

An MDRAM can be viewed as an array of many independent 256 Kbit (32 KByte) DRAMs, -- each with a 32-bit interface -- connected to a common bus internal to the MDRAM. The external interface is simply a buffered version of the internal bus, seen through a bus repeater. The small bank size and the simplicity of the repeater yield extremely short CAS access la-

tency. The independence of bank facilitates overlapping, or "hiding" the RAS access and precharge penalty so that *average* access times will approach the CAS access time.

Embedded applications, using small amounts of DRAM (under 8 MBytes) will frequently benefit from the MDRAM's fine granularity yielding lower cost solutions than even standard, low performance DRAM. MDRAM arrays can be created in increments of 256 KByte. For example, an application *requiring* 2.75 MBytes *can use* precisely 2.75 MBytes of MDRAM rather than incrementing up to 4 MBytes as with any other DRAM.

#### Mul tibank® DRAM (MDRAM®)

128Kx32 to 656Kx32

#### Preliminary Information

#### **MDRAM Organization**

Figure 1 illustrates the internal structure of the MDRAM. The memory is composed of independent and fully functional 32 KByte DRAM banks. The control of each bank is local to each bank rather than centralized.

Address recognition is normally accomplished within the bank so that no external address decoding is required. Programmable bank ID registers are used to map banks to a logical address space. Multiple devices may be cascaded to form larger memory arrays by programming each bank ID register with a unique address. Up to 8 MBytes of memory may be accumulated on a single bus without external address decoding.

Banks are organized in 256 rows by 32 words. Each word is 32 bits wide. All banks are tied to a common internal bus that terminates on a single bus repeater unit at one end of the chip.

Both the internal and external bus consist primarily of a multiplexed address and data bus, a command bus and clock. During data transfer, both clock edges are used for synchronous transfer of 32 bits per clockcycle on only 16 pins. Data mask bits (DM) facilitate byte level write masking.

The bus repeater buffers the internal bus from the external bus. The repeater also contains a phase lock loop (PLL) and a four 1/2 word deep FIFO with programmable latency that guarantees accurate I/O timing.

#### **MDRAM Operation**

A RAS operation (typically called ACTIVATE in SDRAM devices) copies a single row of a *single* bank into its sense amps. Successive RAS/ACTIVATE commands can activate a single bank or multiple banks.

CAS operations (READ or WRITE) proceed with any activated bank with short latency and high bandwidth. READ or WRITE operations continue in a burst, at ascending column addresses, until terminated by a STOP command. Reading or writing past the end of a row (column address 0x1FH) will "wrap" to the beginning of the row.

A bank is deactivated by the PRECHARGE command. PRECHARGE writes the contents of the sense amps

into the memory array -- deactivating the bank. Unlike DRAMs, PRECHARGE is optional when changing banks. READ/WRITE operations may proceed at any activated bank. PRECHARGE may be delayed until another row in an already active bank is to be accessed.

Memory is addressed to the 32-bit word. DM bits facilitate byte-level write masking. Banks have a pre-programmed address at power-on which may be overwritten by a command. Each bank can be treated as a single, independent memory module. Large memory arrays are implemented by programming each bank of a multichip memory to a unique address.

#### Signal Description

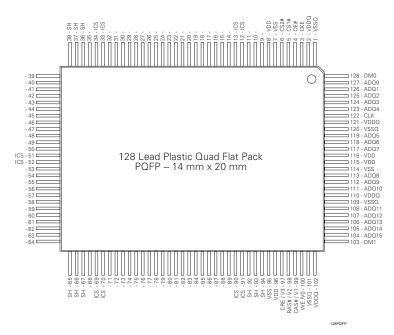

All MDRAM devices share identical packages and pinout. (Fig. 2, 3). There are 26 active signal pins and 12 power/ground pins. All high speed signals are arranged on one side of the package, in order to equalize and reduce PC board trace length, routing capacitance and inductance.

**ADQ[15:0], (In/Out), Address/Data Bus:** These bidirectional pins carry multiplexed address and data. During the command phase of an operation, the ADQ bus carries address information to the MDRAM. The address is sampled on the rising edge of clock.

During the data phase of READ or WRITE the ADQ bus carries 32-bit data words. Data is transferred synchronously, 16 bits at a time, on the rising and falling edge of the clock.

Table 1. Pin Grouping

| Datapath   |    |                          |

|------------|----|--------------------------|

| ADQ[15:0]  | 16 | Multiplexed Address/Data |

| DM[1:0]    | 2  | Write Data Mask          |

| Command    |    |                          |

| CRE or V3  | 1  | Control Register Enable  |

| RAS# or V2 | 1  | Row Address Strobe       |

| CAS# or V1 | 1  | Column Address Strobe    |

| WE or V0   | 1  | Write Enable             |

| Control    |    |                          |

| CLK        | 1  | Clock Input              |

| CKE        | 1  | Clock Enable             |

| OE#        | 1  | Output Enable            |

| CS1#       | 1  | Chip Select 1            |

| CS2#       | 1  | Chip Select 2            |

Total Signals 26

**DM[1:0], (In) Data, Mask:** These signals are used for data masking during the write operation. They are sampled on the rising and falling edge of the clock. A

### Mul tibank® DRAM (MDRAM®)

128Kx32 to 656Kx32

#### Preliminary Information

high on a DM bit prevents the corresponding byte from being written. If data masking is required, all DM signals must be high during the rising and falling edges of the WRITE command phase. If write masking is not required, the DM signals should be tied permanently low.

**CRE, RAS#, CAS#, WE, (In), Command Bus:** These signals collectively named as V[3:0], form the command bus. They are sampled on the rising edge of the clock. The names V[3:0] and the conventional names (CRE, RAS#, CAS# and WE) are used interchangeably in this data-sheet.

**CLK**, **(In)**, **Memory Clock**: All signals except OE# and CS# are synchronously sampled by this clock.

**OE#**, **(In)**, **Output Enable:** This asynchronous control signal can be used to turn around the data bus in systems operating at relatively low frequencies but requiring short access latency. For most applications OE# should be tied permanently low.

**CKE**, **(In)**, **Clock Enable:** This control signal enables the memory clock. CKE is sampled on the rising edge of CLK and is effective on the next rising edge. CKE can be used to freeze the data that is clocked out on the falling edge on the memory clock. For most applications CKE should be permanently tied high.

**CS1#**, **(In)**, **Chip Select 1:** This asynchronous control signal enables or disables the MDRAM. It is useful for memory initialization, power management, and for address decoding of arrays larger than 8 MBytes.

**CS2#**, **(In)**, **Chip Select 2**: This signal is reserved for larger memories with two die in the same package.

VDD/GND (Power): Memory core power supply.

**IOVDD/IOGND (Power):** I/O driver power supply.

**SH, (Passive), Short**: These are No-Connect (NC) pins shorted together.

**ICS, IC Substrate** These pins are connected to the chip substrate and should remain unconnected.

Figure 2. 128 Pin PQFP Pinout

### Mul tibank® DRAM (MDRAM®)

128Kx32 to 656Kx32

#### Prel iminary Information

Figure 3. 68 Pin PLCC Pinout

Note 1: Unlabeled pins are not connected.

Note 2: Adjacent pins marked SH are shorted together but are not connected to the die.

Note 3: Pins labeled ICS are connected to the chip substrate. <u>DO NOT CONNECT EXTERNALLY</u>

### Mul tibank® DRAM (MDRAM®)

128Kx32 to 656Kx32

### Prel iminary Information

#### Table 2. MDRAM Commands

|           | С | R | С | W | x = DON'T CARE           |   |   |   |   |   |       |

|-----------|---|---|---|---|--------------------------|---|---|---|---|---|-------|

|           | R | Α | Α | Ε |                          |   |   |   |   |   |       |

|           | E | S | S |   |                          |   |   |   |   |   |       |

|           |   | # | # |   |                          |   | С | С | О | С |       |

|           | V | V | V | V | Physical Pins: ADQ[15:0] | D | L | Κ | Ε | S |       |

| Operation | 3 | 2 | 1 | 0 | ADQ(15)ADQ(0)            | М | Κ | Ε | # | # | Notes |

**Single Cycle Commands**

| ACTIVATE (2h)  | L | L | Н | L |   |   | Ba | nk A | ddre | ess |      |    |   |   | Ro | w A | ddre | ess |   |   | Х | 1 | Н | Х | L |   |

|----------------|---|---|---|---|---|---|----|------|------|-----|------|----|---|---|----|-----|------|-----|---|---|---|---|---|---|---|---|

| PRECHARGE (3h) | L | L | Η | Н |   |   | Ba | nk A | ddre | ess |      |    | Χ | Χ | Χ  | Х   | Χ    | Χ   | Χ | Χ | Х | 1 | I | Χ | Г |   |

| STOP&PRE (3h)  | L | L | Η | Н | Х | Χ | Χ  | Χ    | Χ    | Χ   | Χ    | Χ  | Χ | Χ | Χ  | Х   | Χ    | Χ   | Χ | Χ | Х | 1 | I | Χ | Г | 1 |

| MODEREGWR (7h) | L | Н | Η | Н | Χ | Χ | Χ  | Χ    | Р    | La  | iten | СУ | L | L | L  | L   | L    | L   | L | Г | Х | 1 | I | Χ | Г |   |

| STOP (Fh)      | Ι | Η | Τ | Н | Х | Χ | Χ  | Χ    | Χ    | Χ   | Χ    | Χ  | Χ | Χ | Χ  | Х   | Χ    | Χ   | Χ | Χ | Х | 1 | Н | Χ | L |   |

**WRITE Command Sequence**

| WRITE (5h) | L | Н | L | Н | Bank Address | Х | Χ | Χ | Column Address | Н  | 1            | Н | Χ | L | 2 |

|------------|---|---|---|---|--------------|---|---|---|----------------|----|--------------|---|---|---|---|

| WRITE (5h) | L | Н | L | Н | D15          |   |   |   | D0             | HL | 1            | Н | Χ | Г | 3 |

| WRITE (5h) | L | Н | L | Н | D31          |   |   |   | D16            | HL | $\downarrow$ | Н | Х | Г | 3 |

**READ Command Sequence**

| READ (4h) | L | Н | L | L | Bank Address | Х    | Х    | Χ    | Column Address | Х | 1                     | Н | Χ | L |     |

|-----------|---|---|---|---|--------------|------|------|------|----------------|---|-----------------------|---|---|---|-----|

| READ (4h) | L | Н | L | L | Hi Impedance | e/Tu | rn A | rour | d              | Х | ↑↓                    | Н | L | L | 4,5 |

| READ (4h) | L | Н | L | L | D15          |      |      |      | D0             | Χ | $\uparrow\downarrow$  | Н | L | L | 5   |

| READ (4h) | L | Н | L | L | D31          |      |      |      | D16            | Х | $\downarrow \uparrow$ | Н | L | L | 5   |

#### **ID Register Write Command Sequence**

| IDREGWR (Dh) | Н | Н | L | Н |   | С   | urrei | nt B | ank   | ID |   | 0 | Х | Х | Х | Х | Χ | Χ | Х | Χ | Х | 1            | Н | Х | L |  |

|--------------|---|---|---|---|---|-----|-------|------|-------|----|---|---|---|---|---|---|---|---|---|---|---|--------------|---|---|---|--|

| STOP (Fh)    | Н | Н | Н | Н |   | - 1 | Vew   | Baı  | nk IE | )  |   | 0 | Х | Χ | Χ | Х | Χ | Χ | Χ | Χ | Х | 1            | Н | Х | L |  |

| STOP (Fh)    | Η | Н | Н | Н | Х | Χ   | Χ     | Χ    | Χ     | Χ  | Х | Χ | Χ | Х | Χ | Х | Χ | Χ | Х | Χ | Χ | $\downarrow$ | Н | Х | L |  |

**Memory Reset Command Sequence**

| MEMRESET (6h) | L | Н | Н | L | Х | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Х | Χ | Х | Χ | Χ | Χ | Н | Н | Х | 1 | Н | Χ | L |  |

|---------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|

| STOP (Fh)     | Τ | Н | Н | Н | Х | Х | Χ | Χ | Χ | Х | Χ | Χ | Х | Χ | Х | Χ | Χ | Χ | Χ | Χ | Х | 1 | Н | Χ | L |  |

| STOP (Fh)     | Η | Н | Н | Н | Χ | Χ | Х | Χ | Χ | Х | Χ | Χ | Χ | Χ | Χ | Χ | Х | Χ | Х | Χ | Х | 1 | Н | Х | L |  |

Powerdown/Memory Disable

|             | _ |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

|-------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|

| xxxx (xH) x | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Н |  |

- Note 1: PRECHARGE interrupting a READ is equivalent to STOP followed by PRECHARGE (STOP&PRE) and affects the bank being read.

Any address forced on ADQ bus is ignored.

- Note 2: If data masking is required all DM signals must be high during the rising and falling edges of the WRITE command phase. If write masking is not required the DM signals should be tied permanently low.

- Note 3: DM[1:0] set masks corresponding data byte. For example, DM[1] high masks D[15:8] on rising clock edges and D[31:24] on falling clock edges.

- Note 4: The READ command phase is followed by a specified number of one-half-clock-period Latency phases.

- Note 5: Latency Value controls which half-word is latched on rising edge of CLK. The first data half-word latches on rising edges when Latency is even.

### Mul tibank® DRAM (MDRAM®)

128Kx32 to 656Kx32

### Prel iminary Information

#### **Command Description**

Ten MDRAM commands are listed on Table 2. The remaining commands are reserved and should never be used. All except four commands are single cycle long. A legal command must be present on the command bus on every clock cycle. A "clock cycle" is from clock rising edge to clock rising edge. All commands are sampled on the rising edge of the clock. All operations begin with a "command/address" phase that is one clock cycle in length.

**MEMRESET [], (3 Cycles):** Initializes the mode register and all ID registers to power up defaults and deactivates (precharges) all banks.

MEMRESET is not data-safe. Data may be lost if all banks are not already precharged.

ACTIVATE [Bank, Row], (1 Cycle): ACTIVATE is similar to RAS in standard DRAM. It loads the contents of the selected row to the sense amplifier latches of that bank. Subsequent READs or WRITES to the activated bank operate on the sense amplifier latches. Before another row in the same memory bank can be selected, a PRECHARGE command must be used to store the data from the sense amplifiers back to the memory cells.

The ACTIVATE command must not be used:

- When TRP timing is violated.

- When the selected bank is already activated.

- Within a READ, WRITE, or IDWRITE operations.

**PRECHARGE [Bank], (1 Cycle):** PRECHARGE copies the sense amp contents to the memory cells of the addressed bank and prepares the bank for the next ACTIVATE/RAS operation. A bank may be precharged even if it is in the deactivated or precharged state.

During READ operations, this command terminates the current operation and executes a precharge to the bank currently in a read state (STOP&PRE). WRITES must be terminated with a STOP. If PRECHARGE is used to terminate a READ, then TRP is measured from the falling edge of the PRECHARGE command cycle to the rising edge of the ACTIVATE command cycle.

The precharge command can be used at any time except:

- To terminate a WRITE

- When it violates Tras (ACTIVATE to PRECHARGE delay).

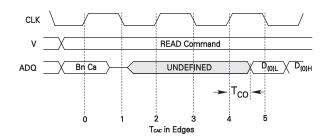

**READ [Bank, Column], (Multicycle):** READ is similar to CAS read in standard DRAM. READ transfers data from the sense amps addressed by the column address, to the output. A READ command is followed by a specified number of one-half-clock-period latency phases and even number data phases. The number of latency phases is programmable and may be even or odd (see Memory Initialization).

After the column access latency, each succeeding clock edge transfers data from ascending column addresses in a burst. A 16-bit value is read each data phase. The READ command must be maintained on the command bus for the duration of the operation. READ terminates with STOP or PRECHARGE. The MDRAM will terminate a READ and will not send data on the ADQ bus if a STOP command is issued immediately after the READ command phase. A burst READ must be terminated with a STOP before another READ command is issued for the same bank but different column.

READs past the end of a row (column address 0x1FH) will "wrap" to the beginning of the row.

The READ command can be used:

- Only on activated banks.

- At any time except when TRCD is violated.

WRITE [Bank, Column], (Multicycle): WRITE transfers data from the ADQ bus to the selected bank and column address. WRITE employs burst transfers. After the one cycle command/address phase, each succeeding clock edge writes to ascending column addresses. A WRITE command phase must always be followed by an even number of data phases of one half-clock period in length. A 16-bit value is written each data phase.

The WRITE command must be maintained on the command bus for the duration of the command phase and data phases. WRITE terminates only with a STOP command. WRITE must be followed by at least two data phases (one 32-bit word) before it can be terminated with a STOP command.

At clock frequencies above 125 MHz, a READ following a WRITE to the same bank or the bank that

### Mul tibank® DRAM (MDRAM®)

128Kx32 to 656Kx32

#### Preliminary Information

shares the same upper seven address bits must have two STOP commands between the last data phase of WRITE and the command phase of READ. WRITEs past the end of a row (column address 0x1FH) will "wrap" to the beginning of the row. The latency setting does not effect WRITE.

The WRITE command can be used:

• At any time except when TRCD is violated.

**STOP [], (1 Cycle):** STOP terminates the current READ/WRITE operation and sets the memory to the idle state without invoking PRECHARGE. Additional READ or WRITE commands to the same bank and row, or to other active banks, can proceed without

new ACTIVATE commands. Repeated STOP commands are equivalent to no-operation (NOP) and hold the memory in an idle state.

The stop command can be used at any time except:

• Immediately after the WRITE command (before any WRITE data phases).

**MODEREGWR [Mode Bits], (1 Cycle):** Mode Register Write initializes the mode register.

**IDREGWR [Old ID, New ID], (2 Cycle):** ID Register Write loads the bank ID register with a new value. This command is used to map memory banks to logical address space.

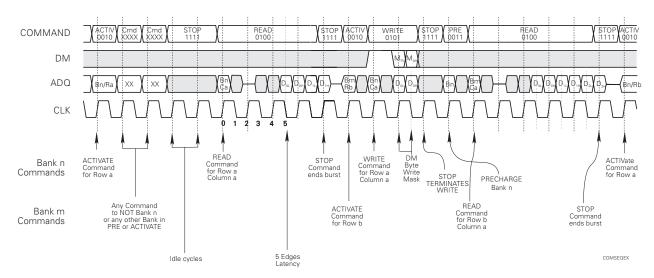

Figure 5. Command Sequence Example

### Mul tibank® DRAM (MDRAM®)

128Kx32 to 656Kx32

#### Preliminary Information

#### **Memory Initialization**

On power up the memory must be initialized with a MEMRESET and MODEREGWR commands.

#### **Mode Register**

The mode register definition is shown in Table 3. On power up, the eight LSBs and PD bit are reset to zero. The Latency Value after power up is undefined. The PD and Latency fields must be initialized by MODEREGWR. PD = "0" is the normal, powered up state. PD = "1" places the memory in power down state by turning off the Phase-Locked-Loop.

**Table 3. Mode Register Definition**

| M[15:12] | M[11] | M[10:8] | M[7:0]        |

|----------|-------|---------|---------------|

| Ignored  | PD    | LATENCY | Reserved Must |

|          |       | VALUE   | be 0          |

MDRAM delivers data on both rising and falling edges of the clock. The latency value can be used to relocate the first 16-bit word of a data burst on a rising or a falling edge of the clock as desired. Figure 5 shows an example at 125MHz with latency value set to 010. Legal latency settings for each device speed grade versus frequency are given in the AC timing parameter section (Table 11).

Table 4. Latency Value

| M10 | M9 | M8 | Tcac in clock edges |

|-----|----|----|---------------------|

| 0   | 0  | 0  | 3                   |

| 0   | 0  | 1  | 4                   |

| 0   | 1  | 0  | 5                   |

| 0   | 1  | 1  | 6                   |

| 1   | 0  | 0  | 7                   |

| 1   | 0  | 1  | 8                   |

| 1   | 1  | 0  | 9                   |

| 1   | 1  | 1  | 10                  |

#### **ID Registers**

The contents of bank ID registers map each bank to logical address space. On power up, the bank ID registers are preset sequentially starting from bank zero. When multiple devices are tied on the same bus, the bank ID registers of all devices must be initialized in order to remap all memory banks to non-overlapping space.

The contents of the ID registers are changed with the IDREGWR command. To prevent IDREGWR command from effecting all the devices on the bus, the Chip Select signals (CS1#, CS2#) can be used to enable only one chip at a time. The bank ID register contents are volatile. The default value will be restored each time power is applied or when the MEMRESET command is executed. Note that the ID register contains 7 bits that correspond to the 7 MSB of two banks, meaning that two banks are programmed at a time and share the same 7 MSB of their ID.

#### **Memory Refresh**

Memory Refresh is accomplished with an ACTIVATE and PRECHARGE (RAS and precharge) operations to every row of every bank every TREF period.

Figure 6. READ with Latency Set to 010

### Mul tibank® DRAM (MDRAM®)

128Kx32 to 656Kx32

### Preliminary Information

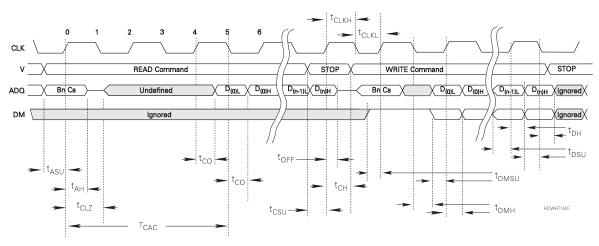

Figure 7. READ and WRITE Timing

Note: The READ or WRITE command on the control bus V[3:0] must be maintained throughout the read/write burst

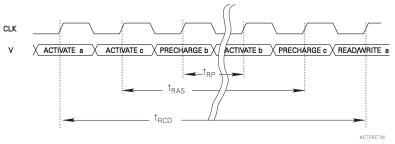

Figure 8. ACTIVATE and PRECHARGE Timing

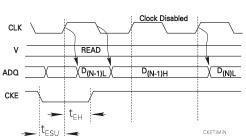

Figure 9. Clock Enable Timing

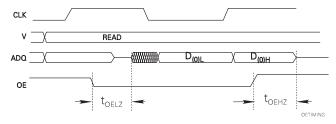

Figure 10: Output Enable Timing

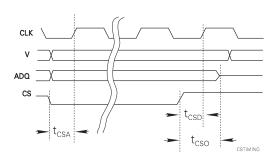

Figure 11. Chip Select Timing

# Mul tibank® DRAM (MDRAM®)

128Kx32 to 656Kx32

### Preliminary Information

**Table 5. Absolute Maximum Ratings**

| Parameter                                                    | Value           |

|--------------------------------------------------------------|-----------------|

| Voltage on Vdd pin relative to GND                           | -1.0V to 7.0V   |

| Voltage on I/O pin relative to GND (During normal operation) | -1.0V to Vdd    |

| Voltage on input pin relative to GND (No Vdd applied)        | -1.0V to 7V     |

| Short-circuit output current, I <sub>OS</sub>                | 20 mA           |

| Operating Temperature, T <sub>OPR</sub>                      | 0 to +70°C      |

| Storage Temperature, T <sub>STG</sub>                        | -55°C to +125°C |

Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should be operated within the limits specified under Recommended Operating Conditions, DC Current Requirements and AC Characteristics.

**Table 6. Recommended Operating Conditions**

| Parameter           | Symbol   | Min.             | Min. Typical |                  | Un | Notes |  |

|---------------------|----------|------------------|--------------|------------------|----|-------|--|

| Supply Voltage (-5) | Vdd      | 4.75             | 5.0          | 5.25             | V  |       |  |

| Supply Voltage (-3) | Vdd      | 3.14             | 3.3          | 3.47             | V  | 1     |  |

| Output Voltage High | $v_{OH}$ |                  | 0.8 x Vddq   |                  | V  | 1     |  |

| Output Voltage Low  | $v_{OL}$ |                  | 0.2 x Vddq   |                  | V  | 1     |  |

| Input Voltage High  | $v_{IH}$ | 0.5 x (Vddq + 1) |              | Vdd              | V  |       |  |

| Input Voltage Low   | $v_IL$   | 0                |              | 0.5 x (Vddq - 1) | V  |       |  |

| Case Temperature    | $T_A$    | 0                |              | 70               | °C |       |  |

Note 1: Output load is 110 ohms to Vddq/2

Table 7. Capacitance T<sub>A</sub> = 25°C, f = 1 MHz, Typical Values

|                               | <u> </u> |        | •       |        |  |  |  |

|-------------------------------|----------|--------|---------|--------|--|--|--|

|                               | MD9      | 00X    | MD91X   |        |  |  |  |

| Pin Group                     | 128PQFP  | 68PLCC | 128PQFP | 68PLCC |  |  |  |

| ADQ I/O Pin Capacitance       | 2.6      | 5      | 4.5     | 7      |  |  |  |

| DM Input Pin Capacitance      | 1.6      | 3      | 2.4     | 4      |  |  |  |

| Clock Input Capacitance       | 1.8      | 3.8    | 3.8     | 6      |  |  |  |

| Input Capacitance (all other) | 1.8      | 3.8    | 3.2     | 6      |  |  |  |

**Table 8. DC Current Requirements**

| Parameter             | Symbol                 | Typical Coi<br>PD=0 | re Current<br>PD=1 | Test Conditions (Vdd=3.6/5.5V, $T_A = 0^{\circ}C$ , f=120MHz, $I_{I/O} = 0$ mA)                    |  |  |  |  |  |  |

|-----------------------|------------------------|---------------------|--------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Operating Current     | l <sub>DD</sub>        | 80/150 mA           |                    | 35% read, 35% write, 30% idle. Read, write and idle conditions are defined below. (No I/O loading) |  |  |  |  |  |  |

| Idle Current          | I <sub>DDIDLE</sub>    | 45/93 mA            | 40/83 mA           | CS=0, CKE=1, V[3:0]=1111 (STOP) IDDIDLE = 13 + .635 ( f                                            |  |  |  |  |  |  |

| Refresh Only current  | I <sub>DDREFRESH</sub> | 15/23mA             | 5/9 mA             | ACTIVATE and PRECH every 2 microseconds, on all remaining cycles CS=1                              |  |  |  |  |  |  |

| Chip Suspend Current  | I <sub>DDSUSPEND</sub> | 15/23 mA            | 5/9 mA             | CKE=1, CS=1, V[3:0]=XXXX on all cycles                                                             |  |  |  |  |  |  |

| Clock Suspend Current | $I_{\mathrm{DDLP}}$    | 10/23 mA            | 1/7 mA             | CKE=0, CS=0, V[3:0]=XXXX on all cycles                                                             |  |  |  |  |  |  |

### Mul tibank® DRAM (MDRAM®)

128Kx32 to 656Kx32

### Preliminary Information

Table 9. AC Characteristics, Five Volt I/O (-5), at Recommended Operating Conditions.

| Speed Grade                  |                  |       | -133  |       | -120  |       | -100  |        |        |

|------------------------------|------------------|-------|-------|-------|-------|-------|-------|--------|--------|

| Parameter                    | Sym              | Min   | Max   | Min   | Max   | Min   | Max   | Units  | Notes: |

| READ to data valid           | t <sub>CAC</sub> |       | 17.3  |       | 19.2  |       | 24.0  | ns     | 5,6    |

| ACTIVATE to READ/WRITE delay | $t_{RCD}$        | 22.5  |       | 25.0  |       | 40.0  |       | ns     | 1,6    |

| ACTIVATE to PRECHARGE delay  | t <sub>RAS</sub> | 37.5  |       | 41.7  |       | 40.0  |       | ns     | 1,6    |

| PRECHARGE to ACTIVATE delay  | t <sub>RP</sub>  | 30.0  |       | 33.3  |       | 40.0  |       | ns     | 1,6    |

| Burst mode READ/WRITE cycle  | t <sub>PC</sub>  | 7.5   |       | 8.3   |       | 10.0  |       | ns     |        |

| CLK frequency                | $f_{CLK}$        |       | 133.3 |       | 120.0 |       | 100.0 | MHz    |        |

| CLK duty cycle               |                  | -10.0 | 10.0  | -10.0 | 10.0  | -10.0 | 10.0  | %      | 2      |

| CLK high level width         | $t_{CLKH}$       | 3.4   | 4.1   | 3.8   | 4.6   | 4.5   | 5.5   | ns     | 2      |

| CLK low level width          | $t_{CLKL}$       | 3.4   | 4.1   | 3.8   | 4.6   | 4.5   | 5.5   | ns     | 2      |

| Command setup time           | $t_{CSU}$        | 1.9   |       | 2.1   |       | 4.0   |       | ns     | 3      |

| Command hold time            | $t_{CH}$         | 1.4   |       | 1.6   |       | 2.5   |       | ns     | 3      |

| CKE setup time               | $t_{ESU}$        | 2.3   |       | 2.6   |       | 3.0   |       | ns     |        |

| CKE hold time                | $t_{EH}$         | 1.4   |       | 1.6   |       | 2.0   |       | ns     |        |

| Address setup time           | t <sub>ASU</sub> | 1.9   |       | 2.1   |       | 4.0   |       | ns     |        |

| Address hold time            | t <sub>AH</sub>  | 1.4   |       | 1.6   |       | 2.0   |       | ns     |        |

| Data setup time              | $t_{DSU}$        | 1.4   |       | 1.6   |       | 2.0   |       | ns     |        |

| Data hold time               | t <sub>DH</sub>  | 1.4   |       | 1.6   |       | 2.0   |       | ns     |        |

| Data Mask setup time         | $t_{DMSU}$       | 0.9   |       | 1.0   |       | 2.0   |       | ns     |        |

| Data Mask hold time          | t <sub>DMH</sub> | 1.9   |       | 2.1   |       | 2.0   |       | ns     |        |

| Refresh period               | t <sub>REF</sub> |       | 16.0  |       | 16.0  |       | 16.0  | ms     |        |

| Clock to data output         | $t_{CO}$         | 0.9   | 2.3   | 1.0   | 2.6   | 1.0   | 3.5   | ns     | 8      |

| READ command to ADQ Lo-Z     | $t_{CLZ}$        | 4.7   |       | 5.2   |       | 5.0   |       | ns     |        |

| Burst STOP/PRE to ADQ Hi-Z   | t <sub>OFF</sub> |       | 5.2   |       | 5.7   |       | 6.5   | ns     |        |

| OE high to ADQ Hi-Z          | $t_{OEHZ}$       | 3.8   |       | 4.2   |       |       | 4.0   | ns     |        |

| OE low to ADQ Lo-Z           | $t_{OELZ}$       | 3.8   |       | 4.2   |       |       | 4.0   | ns     |        |

| Chip select high to clock    | $t_{CSD}$        | 2.8   |       | 3.1   |       |       | 4.0   | ns     |        |

| Chip select low to clock     | $t_{CSA}$        | 3.8   |       | 4.2   |       | 4.0   |       | ns     |        |

| Chip select high to ADQ Hi-Z | $t_{CSO}$        |       | 2.8   |       | 3.1   |       | 4.0   | ns     |        |

| Minimum PLL lock frequency   | $f_{LOCK}$       | 50.0  |       | 50.0  |       | 50.0  |       | MHz    |        |

| Power-up/power-on time       | t <sub>PU</sub>  |       | 10.0  |       | 10.0  |       | 10.0  | ms     | 4      |

| ACTIVATE to READ/WRITE delay | $T_{RCD}$        | 3.0   |       | 3.0   |       | 4.0   |       | Cycles | 1,2    |

| ACTIVATE to PRECHARGE delay  | T <sub>RAS</sub> | 5.0   |       | 5.0   |       | 4.0   |       | Cycles | 1,2    |

| PRECHARGE to ACTIVATE delay  | T <sub>RP</sub>  | 4.0   |       | 4.0   |       | 4.0   |       | Cycles | 1,2    |

<sup>1.</sup> To same bank.

<sup>2.</sup> Fclk = max.

<sup>3. &</sup>quot;Command bus" is CRE, RAS#, CAS# and WE.

<sup>4.</sup> Power on or PD = "1" -> "0", delay to full function.

<sup>5.</sup> To any activated bank.

<sup>6.</sup> Characterized but not tested.

<sup>7.</sup> Separation between group commands (GRPACTIVE or GRPPRE) addressed to the same chip.

<sup>8.</sup> Tested with ½ of ADQ pins switching to Vddq and the other ½ switching to Vssq. Load is 25 pF to Vssq and 110 ohm to Vddq/2

### Mul tibank® DRAM (MDRAM®)

128Kx32 to 656Kx32

### Preliminary Information

Table 10. AC Characteristics, Three Volt (-3), at Recommended Operating Conditions.

| Speed Grade                  |                   |       | -166  |       | 50    | -133  |       |        |        |

|------------------------------|-------------------|-------|-------|-------|-------|-------|-------|--------|--------|

| Parameter                    | Sym               | Min   | Max   | Min   | Max   | Min   | Max   | Units  | Notes: |

| READ to data valid           | $t_{CAC}$         |       | 13.1  |       | 14.5  |       | 16.1  | ns     | 5,6    |

| ACTIVATE to READ/WRITE delay | $t_{RCD}$         | 16.2  |       | 17.0  |       | 18.0  |       | ns     | 1,6    |

| ACTIVATE to PRECHARGE delay  | t <sub>RAS</sub>  | 24.0  |       | 26.0  |       | 27.0  |       | ns     | 1,6    |

| PRECHARGE to ACTIVATE delay  | $t_{RP}$          | 24.0  |       | 26.0  |       | 27.0  |       | ns     | 1,6    |

| Burst mode READ/WRITE cycle  | $t_{PC}$          | 6.0   |       | 6.7   |       | 7.5   |       | ns     |        |

| CLK frequency                | $f_{CLK}$         |       | 166.7 |       | 150.0 |       | 133.3 | MHz    |        |

| CLK duty cycle               |                   | -10.0 | 10.0  | -10.0 | 10.0  | -10.0 | 10.0  | %      | 2      |

| CLK high level width         | $t_{CLKH}$        | 2.7   | 3.3   | 3.0   | 3.7   | 3.4   | 4.1   | ns     | 2      |

| CLK low level width          | $t_{CLKL}$        | 2.7   | 3.3   | 3.0   | 3.7   | 3.4   | 4.1   | ns     | 2      |

| Command setup time           | $t_{CSU}$         | 1.5   |       | 1.7   |       | 1.9   |       | ns     | 3      |

| Command hold time            | t <sub>CH</sub>   | 1.1   |       | 1.3   |       | 1.4   |       | ns     | 3      |

| CKE setup time               | $t_{ESU}$         | 1.9   |       | 2.1   |       | 2.3   |       | ns     |        |

| CKE hold time                | t <sub>EH</sub>   | 1.1   |       | 1.3   |       | 1.4   |       | ns     |        |

| Address setup time           | t <sub>ASU</sub>  | 1.5   |       | 1.7   |       | 1.9   |       | ns     |        |

| Address hold time            | t <sub>AH</sub>   | 1.1   |       | 1.3   |       | 1.4   |       | ns     |        |

| Data setup time              | $t_{DSU}$         | 1.1   |       | 1.3   |       | 1.4   |       | ns     |        |

| Data hold time               | t <sub>DH</sub>   | 1.1   |       | 1.3   |       | 1.4   |       | ns     |        |

| Data Mask setup time         | t <sub>DMSU</sub> | 8.0   |       | 0.8   |       | 0.9   |       | ns     |        |

| Data Mask hold time          | t <sub>DMH</sub>  | 1.5   |       | 1.7   |       | 1.9   |       | ns     |        |

| Refresh period               | t <sub>REF</sub>  |       | 16.0  |       | 16.0  |       | 16.0  | ms     |        |

| Clock to data output         | $t_{CO}$          | 0.8   | 1.9   | 1.0   | 2.1   | 1.0   | 2.3   | ns     | 8      |

| READ command to ADQ Lo-Z     | $t_{CLZ}$         | 3.0   |       | 3.0   |       | 3.0   |       | ns     |        |

| Burst STOP/PRE to ADQ Hi-Z   | t <sub>OFF</sub>  |       | 4.1   |       | 4.6   |       | 5.2   | ns     |        |

| OE high to ADQ Hi-Z          | t <sub>OEHZ</sub> | 3.0   |       | 3.0   |       | 3.0   |       | ns     |        |

| OE low to ADQ Lo-Z           | t <sub>OELZ</sub> | 3.0   |       | 3.0   |       | 3.0   |       | ns     |        |

| Chip select high to clock    | t <sub>CSD</sub>  | 2.3   |       | 2.5   |       | 2.8   |       | ns     |        |

| Chip select low to clock     | t <sub>CSA</sub>  | 3.0   |       | 3.5   |       | 3.5   |       | ns     |        |

| Chip select high to ADQ Hi-Z | t <sub>CSO</sub>  |       | 4.0   |       | 4.0   |       | 4.0   | ns     |        |

| Minimum PLL lock frequency   | $f_{LOCK}$        | 50.0  |       | 50.0  |       | 50.0  |       | MHz    |        |

| Power-up/power-on time       | t <sub>PU</sub>   |       | 1.0   |       | 1.0   |       | 1.0   | ms     | 4      |

| ACTIVATE to READ/WRITE delay | T <sub>RCD</sub>  | 3.0   |       | 3.0   |       | 3.0   |       | Cycles | 1,2    |

| ACTIVATE to PRECHARGE delay  | T <sub>RAS</sub>  | 4.0   |       | 4.0   |       | 4.0   |       | Cycles | 1,2    |

| PRECHARGE to ACTIVATE delay  | T <sub>RP</sub>   | 4.0   |       | 4.0   |       | 4.0   |       | Cycles | 1,2    |

- 1. To same bank.

- 2. Fclk = max.

- 3. "Command bus" is CRE, RAS#, CAS# and WE.

- 4. Power on or PD = "1" -> "0", delay to full function.

- 5. To any activated bank.

- 6. Characterized but not tested.

- 7. Separation between group commands (GRPACTIVE or GRPPRE) addressed to the same chip.

- 8. Tested with ½ of ADQ pins switching to Vddq and the other ½ switching to Vssq. Load is 25 pF to Vssq and 110 ohm to Vddq/2

### Mul tibank® DRAM (MDRAM®)

128Kx32 to 656Kx32

### Preliminary Information

Table 11. MDXXXS - Legal Latency Values

| Spe          | ed Gra   | de           |     | -10             |     |       |  |  |

|--------------|----------|--------------|-----|-----------------|-----|-------|--|--|

| Late         | ncy V    | alue         |     | Frequency Range |     |       |  |  |

| $\downarrow$ | <b>↑</b> | $\downarrow$ | 1   | Min             | Max | Units |  |  |

|              | 001      | 010          |     | 50              | 80  | MHz   |  |  |

|              |          | 010          | 011 | 70              | 100 | MHz   |  |  |

Table 12. MDXXXA - Legal Latency Values

|              |        |              |     |                     |                 |     |     |     |     |     |     | •     |

|--------------|--------|--------------|-----|---------------------|-----------------|-----|-----|-----|-----|-----|-----|-------|

| Spee         | ed Gra | ide          |     | -166 -150 -133 -120 |                 |     |     |     |     |     |     |       |

| Late         | ncy V  | alue         |     |                     | Frequency Range |     |     |     |     |     |     |       |

| $\downarrow$ | 1      | $\downarrow$ | 1   | Min                 | Max             | Min | Max | Min | Max | Min | Max | Units |

| 000          | 001    |              |     | 50                  | 110             | 50  | 100 | 50  | 100 | 50  | 100 | MHz   |

|              | 001    | 010          |     | 50                  | 150             | 50  | 133 | 50  | 133 | 90  | 120 | MHz   |

|              |        | 010          | 011 | 50                  | 166             | 50  | 150 |     |     |     |     | MHz   |

**Note:** The latency value must be selected based on frequency of operation and whether the first read data is to be latched on the falling  $\langle \downarrow \rangle$  or rising ( $\uparrow$ ) edge of the clock. For example: The MDXXXA operating at 125 MHz, with the first read data latched on the falling edge of the clock, must have the latency set to (010).

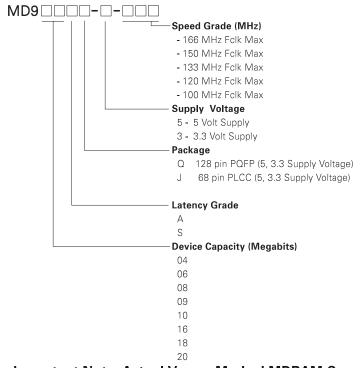

#### **Table 13. Ordering Options**

#### Important Note: Actual Versus Marked MDRAM Capacity

The marked capacity on outside of an MDRAM is the minimum guaranteed capacity, however the actual capacity of any individual device may be larger. This occurs because fractional sizes exist between the marked standard capacities and larger standard size devices may be marked to a smaller capacity.

## Mul tibank® DRAM (MDRAM®)

128Kx32 to 656Kx32

#### Prel iminary Information

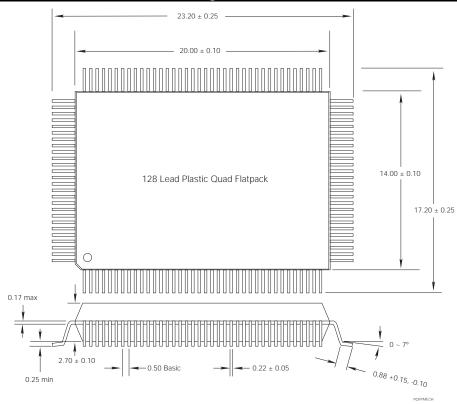

Figure 12. 128 pin PQFP Package Mechanical Dimensions

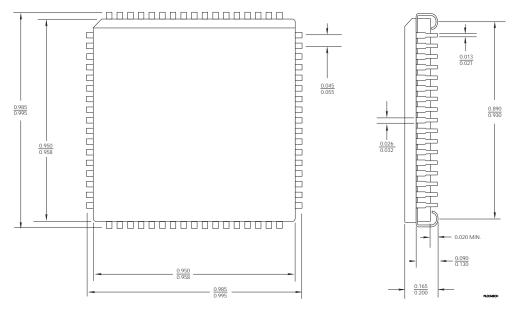

Figure 13. 68 Pin PLCC Package Mechanical Dimensions

# MD904 TO MD920, $\frac{1}{2}$ to $\frac{2}{2}$ MByte Mul tibank® DRAM (MDRAM®)

128Kx32 to 656Kx32

# Preliminary Information

MoSys Incorporated 1020 Stewart Drive Sunnyval e, CA 94086 Tel: (408) 731-1800

MoSys, Mul tibank and MDRAM are registered trademarks of MoSys Incorporated